# The Leader in High Temperature Semiconductor Solutions

Features

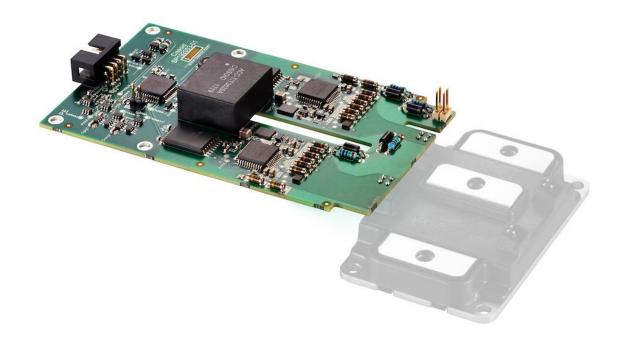

# 1200V High Temperature (125°C) Half-Bridge SiC MOSFET Gate Driver for Wolfspeed XM3 Power Modules

Preliminary Datasheet

- Designed to drive CREE Wolfspeed CAB450M12XM3 1200V/450A SiC MOSFET Power Modules

- Operating temperature: -40°C to 125°C

- Bus voltage: 1200V max

- Isolation: 3600VAC @50Hz (1min)

- 14mm creepage/12mm clearance

- Low parasitic capacitance between primary and high-side: 10pF

- dV/dt immunity > 50kV/µs

- On-board isolated power supply delivering up to 2.5W per channel

- Gate driving voltages: +15V/-4V (3% precision)

- Switching frequency up to 100kHz

Version: 1.1 (see note 1)

- Low inductance gate loop design

- Single power supply: 12V-18V

- RS422 PWM input interface

- Open-drain fault output

- Under voltage lockout (UVLO)

- On-board optional non-overlap generation (via jumper)

- Anti-overlap protection (on PWM inputs)

- Glitch suppressor on PWM inputs

- Active Miller Clamping (AMC)

- Desaturation protection

- Soft-shut-down (SSD)

- Gate-Source short-circuit protection

Note1: Please always refer to the latest datasheet version available at: <u>http://www.cissoid.com/files/files/products/titan/CMT-TIT0697.pdf</u>

# **Ordering Information**

| Product Name | Ordering Reference | Voltage | Marking      |

|--------------|--------------------|---------|--------------|

| CMT-TIT0697  | CMT-TIT0697A       | 1200V   | CMT-TIT0697A |

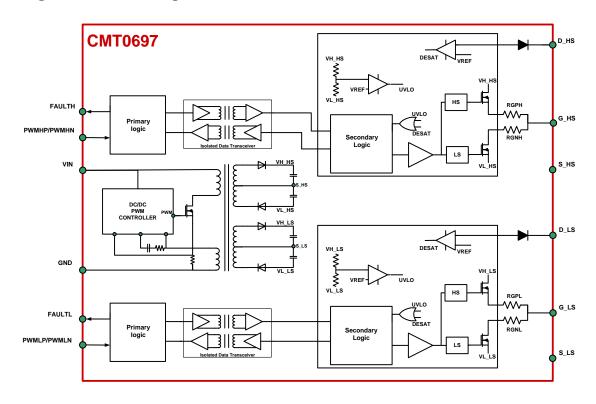

# High level block diagram

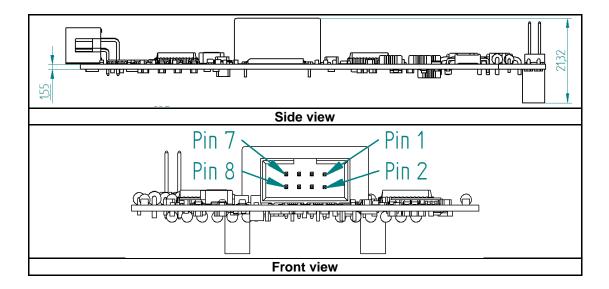

# **IO Description<sup>2</sup>**

| Pin Name | Pin ID | Pin Description                          |

|----------|--------|------------------------------------------|

| PMWLN    | 1      | Negative Low-side PWM<br>control signal  |

| PWMHN    | 2      | Negative High-side PWM control signal    |

| PMWLP    | 3      | Positive Low-side PWM<br>control signal  |

| PWMHP    | 4      | Positive High-side PWM<br>control signal |

| FAULTL   | 5      | Low-side fault                           |

| FAULTH   | 6      | High-side fault                          |

| GND      | 7      | Ground                                   |

| VIN      | 8      | Positive supply                          |

| PE       |        | Chassis connection                       |

|          |        |                                          |

| D_HS     |        | High-side drain sense signal             |

| G_HS     |        | High-side gate signal                    |

| S_HS     |        | High-side source sense signal            |

| G_LS     |        | Low-side gate signal                     |

| S_LS     |        | Low-side source sense signal             |

| VIN         | Positive supply                                                                 |

|-------------|---------------------------------------------------------------------------------|

| VIIN        |                                                                                 |

|             | All other power supplies for driving the gate of the FETs are internally gener- |

| 0.15        | ated by the on-board DC-DC converter                                            |

| GND         | Ground                                                                          |

|             | Reference ground for the supply and the digital IOs.                            |

| PWMHP/PWMHN | Differential input control signals for the high-side driver                     |

|             | These signals control the state of the high-side FET.                           |

|             | When in Local mode (selection by jumper), those signals control both low-side   |

|             | and high-side channels in opposite states with some internally defined non-     |

|             | overlapping delay.                                                              |

| FAULTH      | High-side channel fault output (open drain)                                     |

|             | This signal combines:                                                           |

|             | <ul> <li>The high-side secondary Desaturation fault</li> </ul>                  |

|             | <ul> <li>The high-side secondary UVLO fault</li> </ul>                          |

|             | - The primary fault.                                                            |

|             | In case of fault, FAULTH is set to "0V" for a duration equal to internal timer  |

|             | defined at board level.                                                         |

| PWMLP/PWMLN | Differential input control signal for the low-side driver                       |

|             | The signal controls the state of the low-side FET.                              |

|             | When in Local mode (selection by jumper), those signals have no effect, the     |

|             | low-side FET being control by PWMH and the local non-overlap function.          |

| FAULTL      | Low-side channel fault output (open drain)                                      |

|             | This signal combines:                                                           |

|             | - The low-side secondary Desaturation fault                                     |

|             | - The low-side secondary UVLO fault                                             |

|             | - The primary fault.                                                            |

|             | In case of fault, FAULTL is set to "0V" for a duration equal to internal timer  |

|             | defined at board level.                                                         |

| PE          | Chassis connection                                                              |

|             | A 1000V 1nF capacitance is connected between PE and each of the pins 1 to       |

|             | 8                                                                               |

|             | Ŭ U                                                                             |

<sup>&</sup>lt;sup>2</sup> Refer to section Mechanical characteristics page 13 for more details on connector pinout

### **Absolute Maximum Ratings**

Stressing the board above these absolute maximum ratings could present permanent damage. Exposure to this maximum rating for extended periods may affect the board reliability. These ratings are considered individually (not in combination). If not specified, voltages are related to GND

| Parameter                                 | Min. | Max.  | Units |

|-------------------------------------------|------|-------|-------|

| (VIN-GND)                                 | -0.5 | 18    | V     |

| Voltage transient on S_HS                 |      | 100   | kV/µs |

| Voltage on D_HS, D_LS                     |      | 1200  | V     |

| Output power per gate                     |      | 2.375 | W     |

| Steady Operating Temperature (no airflow) | -40  | 125   | °C    |

| Storage Temperature                       | -40  | 125   | °C    |

### **Electrical Characteristics**

Unless otherwise stated:  $T_j=25^{\circ}$ C. **Bold underlined** values indicate values valid over the whole temperature range (-40°C <  $T_a$  < +125°C).

| Parameter                           | Condition                                                                                           | Min       | Тур | Max        | Units |

|-------------------------------------|-----------------------------------------------------------------------------------------------------|-----------|-----|------------|-------|

| External Power Supply               |                                                                                                     |           |     |            |       |

| External Power Supply VIN           | Versus GND                                                                                          | <u>12</u> |     | <u>18</u>  | V     |

|                                     | VIN=12V, no PWM<br>No fault situation<br>Direct Mode<br>Load: CREE CAB450M12XM3                     |           | 94  |            | mA    |

| I <sub>AVG</sub> (VIN) <sup>3</sup> | VIN=12V; 20 kHz; 50% Duty-Cy-<br>cle<br>No fault situation<br>Local Mode<br>Load: CREE CAB450M12XM3 |           | 179 |            | mA    |

| I <sub>AVG</sub> (VIN) max          | VIN=12V                                                                                             |           |     | <u>500</u> | mA    |

| Parameter                   | Condition                                             | Min        | Тур       | Max | Units |

|-----------------------------|-------------------------------------------------------|------------|-----------|-----|-------|

| Isolation                   |                                                       |            |           |     |       |

| Inter channel Isolation     | S_HS to S_LS<br>(50Hz, 1min)                          | <u>3.6</u> |           |     | kVrms |

| Low-side channel isolation  | S_LS to GND<br>(50Hz, 1min)                           | <u>3.6</u> |           |     | kVrms |

| High-side channel isolation | S_HS to GND<br>(50Hz, 1min)                           | <u>3.6</u> |           |     | kVrms |

| Maximum supported dV/dt     | S_HS to S_LS<br>S_HS to GND<br>(guaranteed by design) | <u>50</u>  |           |     | kV/µs |

| Parasitic capacitance       | Between High-Side and Primary                         |            | <u>10</u> |     | pF    |

| Creepage                    | Primary to any secondary<br>Between secondaries       | <u>14</u>  |           |     | mm    |

| Clearance                   | Primary to any secondary<br>Between secondaries       | <u>12</u>  |           |     | mm    |

<sup>&</sup>lt;sup>3</sup> Refer to Board power dissipation section page 10 for more details

#### **Electrical Characteristics**

Unless otherwise stated:  $T_j=25^{\circ}$ C. **Bold underlined** values indicate values valid over the whole temperature range (-40°C <  $T_a$  < +125°C).

| Deremeter                                                              | Condition                                                                             | Min        | T. m     | Max         | Units |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------|----------|-------------|-------|

| Parameter                                                              | Condition                                                                             | IVIIII     | Тур      | Мах         | Units |

| PWML/PWMH inputs                                                       |                                                                                       |            |          |             |       |

| Common mode input level                                                |                                                                                       | <u>-6</u>  |          | <u>+10</u>  | V     |

| Differential input high-threshold voltage                              | Diff(PWMxP,PWMxN)                                                                     | <u>200</u> |          |             | mV    |

| Differential input low-threshold voltage                               | Diff(PWMxP,PWMxN)                                                                     |            |          | <u>-50</u>  | mV    |

| Differential input impedance                                           |                                                                                       |            | 200      |             | Ω     |

| Minimum pulse width                                                    | Configurable via capacitances Cglil (on PWML) and Cglih (on PWMH)                     |            | 50       |             | ns    |

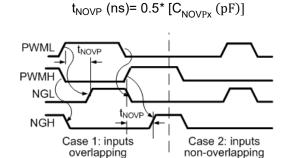

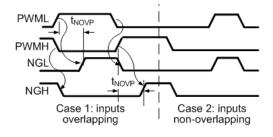

| Anti-overlap duration (t <sub>novp</sub> )                             | Direct Mode<br>Configurable via capacitances Cnovpl<br>(on PWML) and Cnovph (on PWMH) |            | 450      |             | ns    |

| Maximum frequency                                                      |                                                                                       |            |          | <u>100</u>  | kHz   |

| Duty cycle                                                             |                                                                                       | <u>0</u>   |          | <u>100</u>  | %     |

| Propagation delay (PWML/PWMH $\rightarrow$ G_LS/G_HS) (50% to 10%)     | Direct Mode<br>Default settings for glitch suppressor<br>and anti-overlap prevention  |            | 170      |             | ns    |

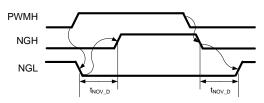

| Non-overlap duration <sup>4</sup>                                      | Local Mode (configurable via capaci-<br>tance Cnovd)                                  |            | 480      |             | ns    |

| FAULTL/FAULTH open drain outputs                                       |                                                                                       |            |          |             |       |

| On resistance                                                          | Applies to FAULTL/FAULTH                                                              |            |          | 25          | Ω     |

| Fault local latching time (at Primary or at Secondary)                 |                                                                                       |            | 14       |             | ms    |

|                                                                        |                                                                                       |            |          |             |       |

| Deveneter                                                              | Condition                                                                             | Min        | <b>T</b> | Max         | Units |

| Parameter<br>G_LS/G_HS Gate driver outputs                             | Condition                                                                             | Min        | Тур      | Мах         | Units |

| High level                                                             |                                                                                       | 14.5       | 15       | 15.5        | V     |

| Low level                                                              |                                                                                       | -4.2       | -4       | -3.8        | V     |

| Maximum average output load current                                    |                                                                                       | -4.2       | 7        | 125         | mA    |

| Peak output current                                                    | Rgate on=Rgate off= 0Ω                                                                | 10         |          | 120         | A     |

| Rgate_on                                                               |                                                                                       | 10         | 1        |             | Ω     |

| Rgate off                                                              |                                                                                       |            | 1        |             | Ω     |

| Gate-Source resistance                                                 |                                                                                       |            | 100      |             | kΩ    |

| Active Miller Clamp (AMC) transistor R <sub>dson</sub>                 |                                                                                       |            | 33       |             | mΩ    |

| D_LS/D_HS Desaturation Monitoring in                                   |                                                                                       | l          | 55       |             | 11132 |

|                                                                        |                                                                                       |            |          | 1000        |       |

| Voltage range                                                          |                                                                                       | <u>0</u>   |          | <u>1200</u> | V     |

| Deremeter                                                              | Condition                                                                             | Min        | Turn     | Max         | Units |

| Parameter                                                              |                                                                                       | Min        | Тур      | Мах         | Units |

| Under-voltage Lockout on primary sup                                   |                                                                                       |            | 0.75     |             |       |

| UVLO_P High Threshold                                                  |                                                                                       |            | 9.75     |             | V     |

| UVLO_P Low Threshold                                                   |                                                                                       |            | 8.2      |             | V     |

| Under-voltage Lockout on secondary s                                   | upplies (VDD_L-VSS_L)/ (VDD_H-VSS_F                                                   |            |          |             | N     |

| UVLO_S High Threshold                                                  |                                                                                       |            | 17.5     |             | V     |

| UVLO_S Low Threshold                                                   |                                                                                       | 1          | 16.2     | l           | V     |

| Desaturation detection                                                 |                                                                                       | 1          |          |             |       |

| Threshold on D_LS/D_HS                                                 | D_LS/D_HS wrt to S_LS/S_HS<br>(configurable via resistance Rdesatx)                   |            | 5.94     |             | V     |

| Desaturation Blanking time                                             | Configurable via capacitance Cdesatdx<br>(68pF Cdesatdx installed)                    |            | 1        |             | μs    |

| Delay from desaturation detection to<br>G_LS/G_HS starting to turn off |                                                                                       |            | 350      |             | ns    |

| G I S/G HS turn-off time after desatura-                               | From 15/(to 0)/                                                                       |            |          |             |       |

From 15V to 0V

Load: CAB450M12XM3

tion detection

Start-up Start-up time

G\_LS/G\_HS turn-off time after desatura-

Soft Shutdown (SSD) resistor

μs

Ω

ms

1

15

30

<sup>&</sup>lt;sup>4</sup> Non-overlap delay includes glitch suppressor delay; 10pF parasitic capacitance to be added to Cnovd

# **Circuit Functionality**

## Description

CMT-TIT0697 board is a Half-Bridge gate driver board meant to drive CREE Wolfspeed CAB450M12XM3 modules

Its main features are:

- Isolated data transmission (robust to high dV/dt) (data and fault) on both high and low side channels

- Adjustable fault timer with automatic restart

- Safe start-up sequence through monitoring of the main supply (UVLO) and of the voltage regulators output (through Power-Good function)

- Permanent and programmable Under-Voltage Lockout (UVLO) monitoring on external and internally generated power switch supplies

- Desaturation detection function with programmable blanking time and threshold protecting power switches in case of abnormal current levels

- Soft-Shutdown transistor and control performing power device graceful shutdown in case of fault and so preventing too high dl/dt in the power stage

- Active Miller Clamping (AMC)

- Flyback DC-DC convertor with cycleby-cycle current limit for short circuit protection

- High-precision (typ 3%) high-level gate voltage generation

- Differential RS422 PWM inputs

- Open-drain low-ohmic (typ. 25Ω) FAULT output

- Support of 2 separate incoming PWM channels and of locally generated nonoverlapped PWM signals

- Configurable 50ns (typ) spike filter on incoming PWM signal for enhanced noise robustness

- Configurable 200ns (typ) anti-overlap protection on incoming PWM signals

- Gate-2-Source short-circuit protection

# Under-Voltage Lockout (UVLO)

CMT-TIT0697 board monitors constantly:

- VIN power supply

- High-side secondary supplies (typ +15V/-4V)

- Low-side secondary supplies (typ +15V/-4V)

At primary side, the monitored power supply is "VIN-GND"; to avoid oscillation when (VIN-GND) is close to the UVLO threshold, a hysteresis is implemented.

At each secondary side, the monitored power supply is "VDD\_L-VSS\_L"/ "VDD\_H-VSS\_H"; to avoid oscillation when (VDD\_x-VSS\_x) is close to the UVLO threshold, a hysteresis is implemented.

Refer to the chapter Fault Management/LED status for details about fault behavior and management.

## **On-board power supplies**

The on-board isolated power supply is a regulated flyback DC-DC converter providing both channels with the positive and negative supply voltages required to drive the power FETs. It offers high voltage isolation between the channels, high dV/dt sustainability and very low parasitic capacitance. Cycle-by-cycle current monitoring at primary side is implemented to protect the board against short-circuit.

High accuracy (typ 3%) is achieved on all secondary positive supplies.

## Interface towards controller

#### PWM inputs

PWML and PWMH input interface is based on RS422 differential receivers to increase noise immunity on those incoming signals. are high impedance inputs.

CMT-TIT0697 board implements 2 protection functions on the PWM data paths:

Anti-glitch: any negative or positive glitch on PWML/PMWH signals smaller than a programmed value is ignored by the board; this is increasing immunity of incoming signals against external noise; the signals are delayed by the corresponding anti-glitch time

$t_{MINPW}$  (ns)= 0.5\* [ $C_{GIIX}$  (pF)]

- Anti-overlap: this circuit prevents PWML and PMWH to be active at the same time by forcing an internal nonoverlap time; if PWML and PWMH are not overlapping by more than the internally programmed time, they are not delayed internally. If PWML and PWMH are active for a long period, both gate outputs are forced to zero until one of the inputs goes to zero.

#### FAULT outputs

The output buffers operate as an opendrain driver with a very low Ron resistance (typ.  $25\Omega$ ), enabling the use of low value pull-up resistance for increased noise immunity.

## Isolated data transmission

CMT-TIT0697 board uses integrated digital isolators. Those devices provide isolation, immunity against high dV/dt and low parasitic capacitance.

In case no power supply is present at the secondary side, a fault is generated at the primary side.

# **Desaturation detection**

The purpose of the desaturation function is to detect that the voltage at the drain of the power switch, in "ON" state, is higher than a given threshold. This informs the logic part of the system about possible damage of the power arm (e.g. a short circuit at the arm level leading to an overcurrent in the power switch).

The sensing of the power device drain voltage is performed through a high voltage

sensing diode whom cathode is connected to the power switch drain and whom anode is connected to a current source (typ 2mA) and a sensing circuit.

The desaturation threshold (on D\_LS/D\_HS nodes) is configured by onboard resistors and can be tuned according to the table below.

| Rdesat         | Desat threshold (V) |       |  |

|----------------|---------------------|-------|--|

| value          | 25°C                | 125°C |  |

| 0ΚΩ            | 1.18                | 1.47  |  |

| 5ΚΩ            | 2.6                 | 2.86  |  |

| 10KΩ           | 4.0                 | 4.26  |  |

| 16KΩ (default) | 5.7                 | 5.94  |  |

| 20kΩ           | 6.8                 | 7.06  |  |

| 30kΩ           | 9.66                | 9.86  |  |

At system level, the de-saturation detection should only be taken into account after a defined time following the low-to-high transition on the power device gate. This "blanking" time  $t_{\text{DESAT}_D}$  is implemented and adjusted by an on-board capacitor  $C_{\text{DESATD}}$  (68pF installed) and can be calculated as follows:

$t_{\text{DESATD}}$  (ns)= 14\* [ $C_{\text{DESATD}}$  (pF) + 7]

If after t<sub>DESAT\_D</sub> time, the DESAT comparator output indicates that D\_LS/D\_LS level is higher than the programmed threshold value, an internal DESAT fault is generated. Refer to the chapter Fault Management/LED status for details about fault behavior and management.

When the desaturation fault is detected, the power module gate is gracefully discharged thanks to the Soft-Shutdown circuit to avoid high dl/dt at power module turn-off

Low-side drain voltage is sensed directly on the PCB while for high-side drain voltage, pin header connector is available (for connection towards CREE Wolfspeed power module.

# **Active Miller Clamping**

In case of high positive dV/dt and despite the negative drive of the power module gate, a parasitic turn-on of the gate could take place, inducing shoot-through current on the power arm.

To prevent this, CMT-TIT0697 board implements an Active Miller Clamping function by bypassing the gate resistance with a low ohmic path (implemented with a transistor) when the gate is driven negative. This transistor also helps to limit the amplitude of negative kick on the power module gate in case of negative dV/dt.

### Fault Management/LED status

At primary side, fault is generated by any of those situations:

- Main power supply (VIN) is below the UVLO threshold

- Primary linear voltage regulator (generating the 5V output required by the on-board logic) is below the internal Power Good level

Those faults are internally combined to generate a unique fault signal. This internal fault signal is latched for 14msec.

While the fault is latched:

- Both FAULTL/FAULTH pins are tied to "0"

- Both power switches are turned off

- On board DC-DC converter is off

After the predefined latch time period, CMT-TIT0697 board will attempt to return to normal operation:

- If the fault is still present, CMT-TIT0697 board will stay in the fault state till the fault disappears

- If the fault disappeared (e.g. temporary UVLO situation), CMT-TIT0697 board will go out of FAULT state and return to normal operation (DC-DC converter turned on and data paths active); still, on the PWM path, transition to normal operation will happen on the next positive edge of the incoming PWM signal.

The primary fault state is combined with the faults returned by the secondary devices according to Table 1.

| Prim  | Low-   | High-  | FAULTL   | FAULTH   |

|-------|--------|--------|----------|----------|

| fault | side   | side   |          |          |

|       | fault  | fault  |          |          |

| No    | No     | No     | No fault | No fault |

| No    | Yes    | No     | Fault    | No fault |

| No    | No     | Yes    | No fault | Fault    |

| No    | Yes    | Yes    | Fault    | Fault    |

| Yes   | Yes or | Yes or | Fault    | Fault    |

|       | No     | No     |          |          |

Table 1: FAULT aggregation table

At each of the secondary side, fault is generated by any of those situations:

- Power supply is below the UVLO threshold

- Secondary voltage regulator (5V) output voltage is below the Power-Good threshold

- Desaturation situation is detected by the DESAT comparator

Those faults are internally combined to generate a unique fault signal. This internal fault signal is latched for 14msec.

While the fault is latched, the gate driver is turned off. At the transition between "no fault" and "fault" situation, the gate driver circuit is gracefully shut down (Soft Shut-Down).

After the predefined latch time period, the gate driver circuit returns to normal operation:

- If the fault is still present, the gate driver is kept turned off till the fault disappears

- If the fault disappeared (e.g. temporary UVLO situation), normal operation will resume on the next positive edge of incoming PWM signal

2 LEDs are present on the CMT-TIT0697 board and are reflecting board status as follows:

| State                            | LED1  |       | LE    | D2    |

|----------------------------------|-------|-------|-------|-------|

|                                  | State | Color | State | Color |

| No supply                        | Off   | None  | Off   | None  |

| Operational                      | On    | Green | Off   | None  |

| Primary or<br>secondary<br>fault | On    | Green | On    | Red   |

### Modes of operation

CMT-TIT0697 board offers 2 modes of operation:

- Direct Mode: PWML and PWMH are generated independently outside CMT-TIT0697 board. In this case, proper non overlapping must be generated externally. Glitch filter is active on both PWM incoming signals

- Local Mode: PWML and PWMH are generated out of one input signal (PWMH) and proper non overlapping timing is managed locally on the CMT-TIT0697 board (cfr Figure 1). Glitch filter is active on PWMH signal. In this mode, at board start-up, both gate signals are inactive. However, when PWMH is low, low-side gate is "high" while high-side gate is "low".

#### Figure 1: Local Mode operation

Use of anti-overlap function The drawback of using the Local Mode is that it is not possible to force the 2 gate signals to "low".

When using the board in Direct Mode and applying PWMH and PWML being exactly the opposite of each other, the board will generate 2 gate signals which are nonoverlapped by a time equal to tnovp (see figure below) but when forcing the 2 PWM signals to "low", the 2 gates signals will be forced to "low".

The choice between those 2 modes of operation is made via the jumper JP1.

When in Local Mode, an on-board capacitance (Cnovd) defines the non-overlap delay according to following formula:

$t_{NOV D}$  (ns)=5.5 \*  $C_{NOVD}$ (pF)

### Board power dissipation

Current consumption of the CMT-TIT0697 board (Vin=12V) driving one CREE Wolfspeed CAB450M12XM3 module can be computed as follows:

$$in = 94mAtyp + 4.55 * Fs$$

Where:

Ι

- lin is the input current (in mA) (wrt to Vin = 12V)

- Fs: Switching frequency (in kHz)

The duty cycle of the PWML/PWMH signals has almost no influence on the current consumption of the CMT-TIT0697 board (assuming PWML and PWMH duty cycles are complementary).

To stay within specifications of the internal secondary voltages, the maximum average lin current should be 500 mA (for Vin =12V).

# **Dynamic behavior**

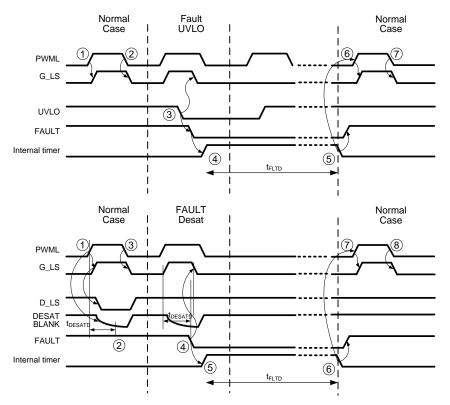

Figure 2 illustrates the CMT-TIT0697 low-side driver dynamic behavior in normal operation and fault conditions.

Figure 2: Timing diagram CMT-TIT0697 low-side driver behaviour

#### In Normal operation

on PWML rising edge (1), rising edge is generated on G\_LS (after propagation delay through CMT-TIT0697 board).

After rising edge on G\_LS, low-side power module is turned ON and midpoint node is going to "0" state (voltage equals to Ron \* current flowing through the power device). D\_LS node is also pulled down and after blanking time (t<sub>DESAT\_D</sub>), no desaturation fault is detected and FAULTL remains high.

on PWML falling edge (2), falling edge is generated on G\_LS (after propagation delay through CMT-TIT0697 board) After falling edge on G\_LS, the low-side power device is turned OFF.

#### In DESAT fault situation

on PWML rising edge (3), rising edge is generated on G\_LS (after propagation delay through CMT-TIT0697 board) After rising edge on G\_LS, low-side power module is turned ON; because of a desaturation fault, D\_LS node does not reach its normal "0" level. Thanks to the DESAT comparator, CMT-TIT0697 board detects this fault situation and turns off gracefully G\_LS. Power device is turned off. FAULTL signal is pulled down. Fault is cleared after fault timer expiry.

#### In UVLO fault situation

UVLO status is monitored inside the secondary devices (and inside primary device as well; for clarity, only secondary UVLO situation is described here). When UVLO comparator (5) detects an under-voltage situation, G\_LS is gracefully shut down FAULTL signal is pulled down. Fault is cleared after fault timer expiry.

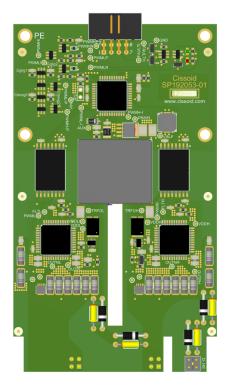

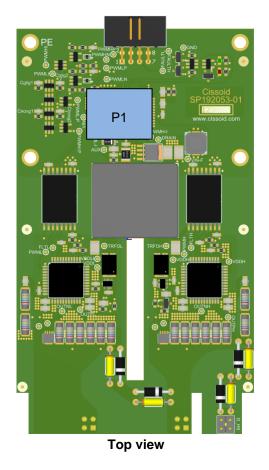

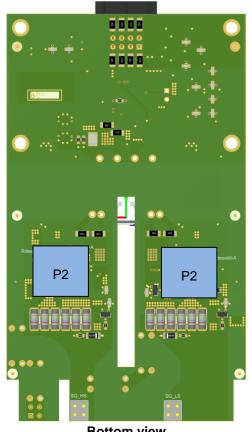

# **Settings Management**

| Function                      | Position<br>on PCB | Component<br>name | Component location | Settings                                                                                                               |

|-------------------------------|--------------------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|

| Direct/Local<br>Mode          | P1                 | JP2 (top)         |                    | Jumper not present: Direct<br>mode<br>Jumper present: Local mode                                                       |

| Non-overlap<br>time           |                    | Cnovd (top)       |                    | t <sub>NOV_D</sub> (ns)=5.5 * C <sub>NOVD</sub> (pF)                                                                   |

| Desaturation<br>threshold     |                    | Rdesat2           | Rdesat2 Cdesat     | Cfr section Desaturation de-                                                                                           |

| Desaturation<br>blanking time | P2                 | Cdesat            |                    | tection<br>Adaptations to be done on<br>both high and low sides.<br>Component positions are the<br>same for both sides |

**Bottom view**

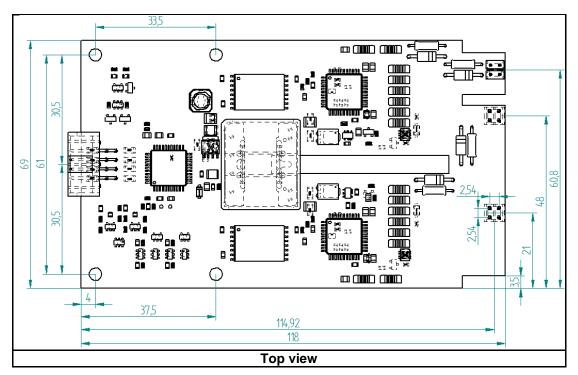

# **Mechanical characteristics**

All dimensions in mm.

### Contact

#### CISSOID S.A.

| Headquarters and contact EMEA: | CISSOID S.A. – Rue Francqui, 3 – 1435 Mont Saint Guibert - Belgium<br>T : +32 10 48 92 10 - F: +32 10 88 98 75<br>Email: <u>sales@cissoid.com</u> |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Sales<br>Representatives:      | Visit our website: <u>http://www.cissoid.com</u>                                                                                                  |

### Disclaimer

Neither CISSOID, nor any of its directors, employees or affiliates make any representations or extend any warranties of any kind, either express or implied, including but not limited to warranties of merchantability, fitness for a particular purpose, and the absence of latent or other defects, whether or not discoverable. In no event shall CISSOID, its directors, employees and affiliates be liable for direct, indirect, special, incidental or consequential damages of any kind arising out of the use of its circuits and their documentation, even if they have been advised of the possibility of such a damage. The circuits are provided "as is". CISSOID has no obligation to provide maintenance, support, updates, or modifications.