# LS0502SCD33S

Single Cell Super Capacitor Protection IC for Backup Power Applications

### HF RoHS 🗭

#### **Features and Benefits**

- 2.5 V to 5.5 V System Voltage

- 18 V Input Rating with Overvoltage Protection

- Programmable 1.1 V to 5.3 V Cap Voltage Range

- Programmable Super Capacitor Charge Current

- Programmable Input Overcurrent Protection

- Up to 2 A Discharge Current

- Programmable Voltage and Current Thresholds

- ±2 % Threshold Accuracy

- 2.5 µA Ready Quiescent Current

- Small Solution Size

- DFN Package

#### Description

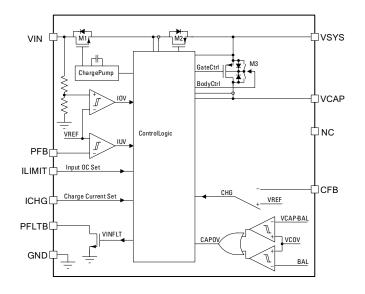

The LS0502SCD33S is a complete solution for system with backup storage capacitor or capacitor bank. It integrates input overvoltage, overcurrent protection circuit, a reverse blocking switch and super capacitor charging control circuit.

When the main supply is present and above the minimum system supply voltage, system will draw power from input supply. At the same time, integrated linear charger charges the storage element at up to 300 mA current. Once the storage element is charged, the circuit draws only 2.5  $\mu$ A of current while it maintains the super capacitor or other storage element in its ready state. When the main supply is removed, the integrated reverse blocking switch will block current flow from system rail to input. The linear charger will be turned on to provide power to system rail with low resistance path with up to 2 A current.

The LS0502SCD33S is externally programmable for input current limit, input overvoltage, charge current limit, and charge voltage limit. It provides a flag signal when input supply is unplugged so that main system can taking action. LS0502SCD33S is available in DFN3X3-10 package.

#### **Applications**

- Handheld Industrial Equipment

- Dash Camera

- IoT

- Smart Meter

- Portable Device with Removable Battery

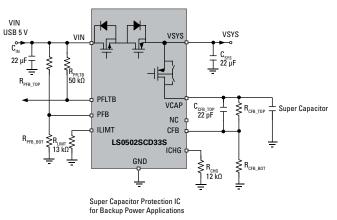

### **Typical Applications**

**Functional Block Diagram**

#### © 2024 Littelfuse, Inc. Specifications are subject to change without notice. Revised: FW.04/02/24

## **LS0502SCD33S** Single Cell Super Capacitor Protection IC for Backup Power Applications

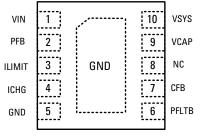

### **Pinout Designation**

Exposed Pad on Backside

| Pin # | Pin Name | Description                                                                                                                                                                                                                                                                                                                                  |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VIN      | Input power supply. Connect to a 5 V system supply rail and bypass with a 10 $\mu F$ capacitor to GND                                                                                                                                                                                                                                        |

| 2     | PFB      | Input voltage sensing input. Connect to the center point of a resistor divider from VIN to GND. It is compared with internal 1.2 V reference. When PFB is below 1.2 V, PFLTB will pull high to indicate input power failure                                                                                                                  |

| 3     | ILIMT    | Input overcurrent protection setting pin. Connect a resistor to ground the set the input overcurrent protection level. If ILIMT is short to GND, input current limit is set to 3 A. If ILIMT is floating, input current limit is 0 A. The limit current is determined by the equation: $ILIMT = 30 \text{ A}^* \text{k}\Omega/\text{RLIMIT}$ |

| 4     | ICHG     | Charge current input. This pin sets the maximum current level for charging super capacitor. The charger current recommend <350 mA ( $R_{CHG}$ >10 k)<br>The charge current is determined by the equation: ICHG = 3.3 A*k $\Omega/R_{CHG}$                                                                                                    |

| 5     | GND      | Ground                                                                                                                                                                                                                                                                                                                                       |

| 6     | PFLTB    | Power fault bar.<br>Open-drain input power failure indicator. PFLTB goes low when the PFB drop below 1.2 V or (VIN-VSYS) exceed 360<br>mV (VSYS to ground short-circuit). Connect to an external pull up resistor.                                                                                                                           |

| 7     | CFB      | VCAP feedback. Connect to the upper point of a resistor divider from VCAP to GND. Part stops charging super capacitor when CFB voltage is above 1.1 V $$                                                                                                                                                                                     |

| 8     | NC       | No connection                                                                                                                                                                                                                                                                                                                                |

| 9     | VCAP     | Super cap. connect to top point of two super cap stacks                                                                                                                                                                                                                                                                                      |

| 10    | VSYS     | Supply rail for internal system. Power is draw from VIN when valid input supply is present. When input power failed, power will be provided by super capacitor connected to VCAP                                                                                                                                                             |

| EP    | EP       | Note: EP use conductive glue and GND PAD has no down bonding                                                                                                                                                                                                                                                                                 |

# LS0502SCD33S

Single Cell Super Capacitor Protection IC for Backup Power Applications

#### **Absolute Maximum Rating (Reference to GND)**

| Symbol                            | Value            | Units |

|-----------------------------------|------------------|-------|

| VCAP, VSYS, PFLTB to GND          | -0.3 to +6       | V     |

| VIN to GND                        | -0.3 to +18      | V     |

| CFB to GND                        | -0.3 to VCAP+0.3 | V     |

| PFB, ILIMT, ICHG to GND           | -0.3 to VSYS+0.3 | V     |

| ESD                               | Class 2          | -     |

| Lead Temperature (Soldering 10 s) | 260              | °C    |

| Junction Temperature Range        | -40 to +150      | °C    |

| Storage Temperature Range         | -65 to +150      | °C    |

\* Notes:Stress exceeding those listed "Absolute Maximum Ratings" may damage the device.

#### **Thermal information**

| Symbol                                   | Value | Units |

|------------------------------------------|-------|-------|

| Maximum Power Dissipation (T_A = 25 °C ) | 3.3   | W     |

| Thermal Resistance ( $\theta_{JA}$ )     | 53    | °C/W  |

| Thermal Resistance ( $\theta_{JC}$ )     | 25    | °C/W  |

Note1: Measured on JESD51-7, 4-Layer PCB.

Note 2: The maximum allowable power dissipation is a function of the maximum junction temperature  $T_{J,MAW}$  the junction to ambient thermal resistance  $\theta_{JM}$  and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{D,MAW} = (T_{J,MAW} T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

#### **Recommend Operating Conditions**

| Symbol                      | Value        | Units |

|-----------------------------|--------------|-------|

| Input Voltage (VIN)         | +2.5 to +5.5 | V     |

| Cap Voltage (VCAP)          | +0.8 to +5.4 | V     |

| Operating Temperature Range | -40 to +85   | °C    |

| Junction Temperature Range  | -40 to +125  | °C    |

\* Notes: The device is not guaranteed to function outside of the recommended operating conditions.

#### Electrical Characteristics (T<sub>A</sub> = +25 °C, VIN = 5 V, VCAP = 5 V, unless otherwise specified) Note 1

| Parameter                                                     | Test Conditions                | Min  | Тур  | Max  | Unit |

|---------------------------------------------------------------|--------------------------------|------|------|------|------|

| Input Voltage Range                                           |                                | 3.3  |      | 5.5  | V    |

| VSYS Charging Supply Current                                  | PFB>1.2 V, VIN = 5 V           |      | 650  |      | μA   |

| VSYS Backup Supply Current                                    | PFB = 0, VCAP = 5 V            |      | 1.5  |      | μA   |

| VCAP UVLO Threshold                                           | VCAP falling                   | 1.45 | 1.65 | 1.85 | V    |

| VCAP UVLO Hysteresis                                          |                                |      | 200  |      | mV   |

| INPUT OVP OCP Switch                                          |                                |      |      |      |      |

| Input Overvoltage Protection Threshold voltage                | VIN Rising                     | 5.6  | 6.0  | 6.4  | V    |

| Input Overvoltage Hysteresis                                  |                                |      | 0.4  |      | V    |

| Input Overcurrent level                                       | R <sub>ILIMT</sub> = 25.5 kΩ   | 0.96 | 1.20 | 1.44 | А    |

| Max Input Overcurrent Level                                   | VIN>4.2 V,ILIMT connect to GND |      | 3.0  |      | А    |

| Input Overvoltage Switch Rdson                                |                                |      | 0.1  |      | Ω    |

| Ideal Diode                                                   |                                |      |      |      |      |

| Drain Source regulation voltage                               |                                |      | 25   |      | mV   |

| Source Drain fast reverse blocking threshold voltage (Note 2) |                                |      | -20  |      | mV   |

| PMOS Rdson                                                    |                                |      | 50   |      | mΩ   |

| PMOS Leakage Current                                          |                                |      |      | 0.1  | μA   |

#### Electrical Characteristics (T<sub>A</sub> = +25 °C, VIN = 5 V, VCAP = 5 V, unless otherwise specified) Note 1

| Parameter                                                             | Test Conditions                                 | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------------------|-------------------------------------------------|------|------|------|------|

| Super Capacitor Charger/Discharger                                    |                                                 |      |      |      |      |

| V <sub>CFB</sub> Threshold Voltage to Stop Charging                   |                                                 | 1.04 | 1.08 | 1.12 | V    |

| V <sub>CFB</sub> Hysteresis                                           |                                                 |      | 40   |      | mV   |

| CFB Regulation Reference Voltage                                      |                                                 | 1.05 | 1.1  | 1.15 | V    |

| CFB Leakage Current                                                   |                                                 |      |      | 50   | nA   |

| Charge Current                                                        | $R_{ICHG}$ = 33 kΩ, VCAP = 3 V                  | 75   | 100  | 125  | mA   |

| Charge Current                                                        | $R_{ICHG}$ = 33 kΩ, VCAP = 0 V                  | 30   | 45   | 60   | mA   |

| Charging/Discharging PMOS Rdson                                       |                                                 |      | 100  |      | mΩ   |

| Maximum Capacitor Voltage                                             |                                                 | 4.88 | 5.3  | 5.52 | V    |

| PMOS Body Diode Switch (VCAP-<br>VSYS) Threshold Voltage              | VCAP ramp up from below VSYS                    |      | 100  |      | mV   |

| PMOS Charge Mode and Switch<br>Body V <sub>DS</sub> Threshold Voltage | VCAP ramp down from above VSYS                  |      | 250  |      | mV   |

| VCAP Charge Mode Threshold (VSYS-VCAP) Voltage                        | VCAP ramp down from above VSYS                  |      | 10   |      | mV   |

| VCAP Charge Threshold (VSYS- VCAP) Hysteresis<br>Voltage              | VCAP ramp up from below VSYS                    |      | -100 |      | mV   |

| Input Power Fail Comparator                                           |                                                 |      |      |      |      |

| V <sub>PFB</sub> Threshold Voltage (Falling)                          |                                                 |      | 1.2  |      | V    |

| V <sub>PFB</sub> Hysteresis                                           |                                                 |      | 85   |      | mV   |

| VSYS Power Good Threshold                                             | VIN-VSYS                                        |      | 320  |      | mV   |

| VSYS Power Fail Threshold                                             | VIN-VSYS                                        |      | 560  |      | mV   |

| PFLT Output Low Voltage                                               | I <sub>SINK</sub> = 1 mA                        |      | 100  |      | mV   |

| PFLT High Impedance Leakage                                           | $V_{PFLT} = 5 V$                                |      |      | 0.1  | μA   |

| PFLT Deglitch Time                                                    |                                                 |      | 3.5  |      | ms   |

| Thermal Shutdown Temperature                                          | T <sub>J</sub> rising, 30 °C typical hysteresis |      | 150  |      | °C   |

| Thermal Shutdown Hysteresis                                           |                                                 |      | 30   |      | °C   |

Note 1: Limits are 100 % production testes @  $T_A$  = +25 °C, unless otherwise noted. Limits over the temperature range are guaranteed by design. Note 2: Guaranteed by design, not production tested.

## LS0502SCD33S Single Cell Super Canacitor Protection IC for B

Single Cell Super Capacitor Protection IC for Backup Power Applications

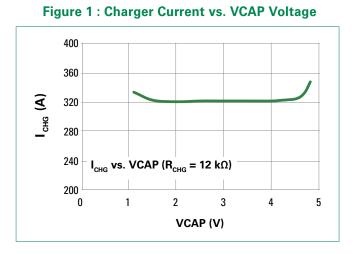

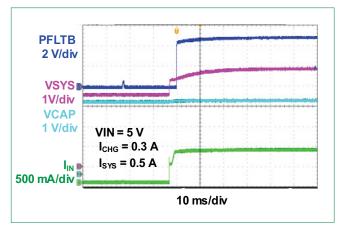

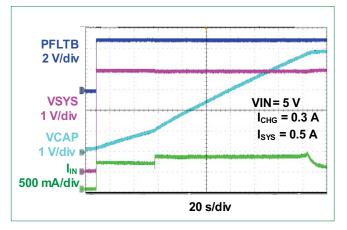

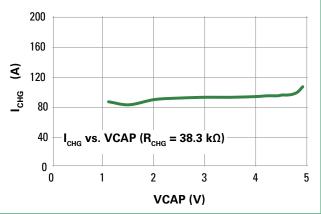

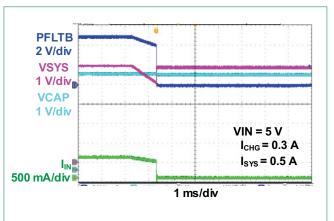

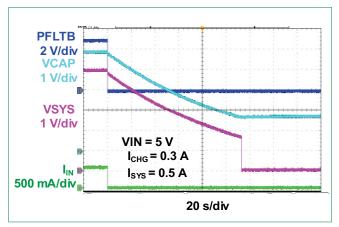

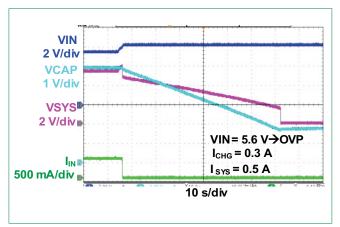

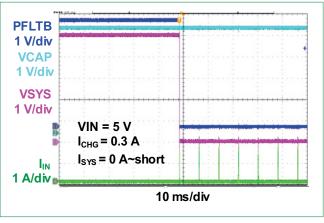

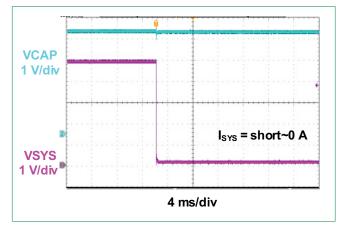

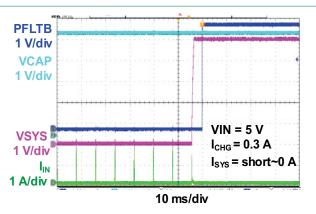

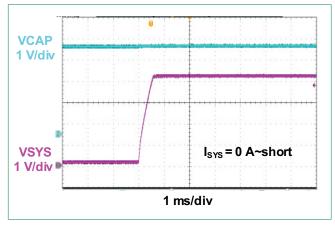

Typical Performance Characteristics (C<sub>IN</sub> = 22  $\mu$ F, C<sub>SYS</sub> = 22  $\mu$ F, R<sub>LIMT</sub> = 13 k $\Omega$ , R<sub>CHG</sub> = 12 k $\Omega$ , T<sub>A</sub> = +25 °C)

#### Figure 3 : Charger VIN Power on

Figure 2 : Charger Current vs. VCAP Voltage

Figure 4 : Charger VIN Power off

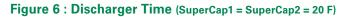

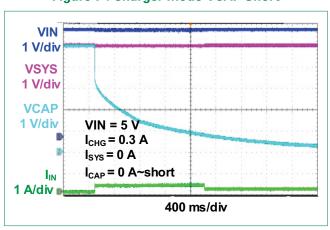

## Figure 7 : Charger Mode VCAP Short

#### Figure 9 : Charger 4VIN Switch to 5VIN (Setting VIN\_UVLO 4.1 V )

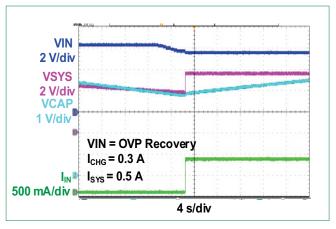

### Figure 11 : VIN OVP Recovery

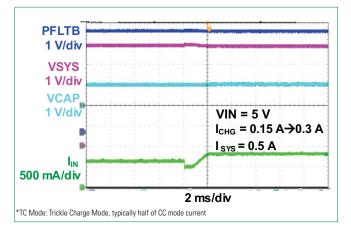

#### Figure 8 : Charger TC Mode\* -> CC Mode

#### Figure 10 : VIN OVP Protection

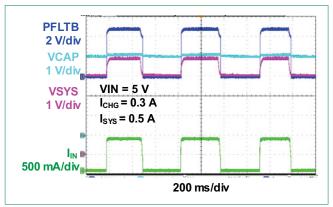

### Figure 12 : Charger Mode VSYS Short

#### Figure 14 : Discharge Mode VSYS Short

### Figure 13 : Charger Mode VSYS Short Recovery

#### Description

For applications which require backup power in harsh environment, Lithium-Ion battery cannot be used due to limited temperature range. Super capacitor with wide operating temperature range and high power/energy density, provides a safe and compact solution. For many systems, the high operating voltage (>3 V) requires a power management system for super capacitor with one cell or use a BOOST converter with inductor. Many systems also require long standby time (weeks of time), this need can only be realized with very low quiescent current.

LS0502SCD33S provides a flexible, integrated and compact storage capacitor or capacitor bank backup solution with extensive protection function to ensure a safe, efficient, compact and low cost solution for these applications. LS0502SCD33S integrates input overvoltage/ current protection to prevent damage to following system. It also integrates an ideal diode for reverse blocking when input voltage is lost.

LS0502SCD33S integrates a linear charger to charge super capacitor with as high as 350 mA current to achieve fast and safe charging. The charging devices also act as power path control switch. When input power is lost, this switch can be turned on to keep the system rail stable in backup mode. In backup mode, quiescent current draw from super capacitor is only 2.5 µA. This ensures very long standby time of the system with low capacitance super capacitor.

LS0502SCD33S integrates a programmable Input voltage monitor. When input voltage drops below certain voltage set by resistor divider connected to PFB pin, a flag signal on PFLTB will inform the following system about the event so that preventative actions can be taken like process and save data in DRAM. LS0502SCD33S also integrates cell monitoring and protection circuit. This circuit monitors voltage for capacitor. During charging mode, if capacitor voltage reaches 5.3 V, charging will be stopped until this fault is gone. Same way, during discharge mode, if the capacitor voltage drop below ground, discharging will be stopped to protect the capacitors.

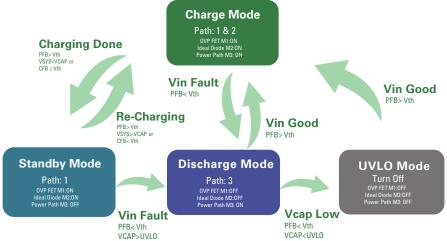

#### Operation

The system should have three states: STANDBY State, CHARGE State, DISCHARGE State and UVLO State.

#### STANDBY State:

1.VCAP > VSYS, VIN is still available and PFB higher than threshold voltage. Or,

2.VCAP reaches setting point by CFB and VIN is still available and PFB higher than threshold. Or,

3.Any of the two super capacitor voltage reaches internal protection point and VIN is still available.

In STANDBY State, M3 FET should be kept OFF. M3 body diode need to be switches according to VSYS VCAP voltage.

#### **CHARGE State:**

VSYS > VCAP, VIN is available and healthy; VCAP is below setting point by CFB. Both super capacitors are below overvoltage protection point. In this state, M3 will turn off with current limit set by ICHG.

Two possible features need to be evaluated:

1. Input DPPM. If input voltage drop and PFB voltage drops close to set point, we can fold back charge current to limit current drain from weak input source

2. Soft charging ending. When VCAP is charged and CFB voltage getting close to set point, we can fold back charge current so that when charge stops, voltage drop on any impedance in series with capacitor doesn't cause oscillation between charge mode/standby mode.

#### **DISCHARGE State:**

When PFB is below threshold, we consider input power source is gone. In this case, OVP FET is turned off. Ideal diode should be turned off too. Power path control FET M3 is turned on to connect VCAP to VSYS. Transition from charge mode or standby mode to discharge mode need to be smooth without huge inrush current, at the same time, it cannot let VSYS drop too much which might cause downstream system to shut down.

In discharge mode, all the bias current is supplied by VCAP. To extend operating time, quiescent current need to be below 1 µA in this case. Circuits need to be alive are: 1. M3 overcurrent detection circuit; 2. UVLO detection circuit for VCAP.

#### UVLO State:

In case the system runs on super capacitor for long time without recharge, eventually VCAP will drop too low to sustain the function of the whole system when VCAP drops too low, we will enter UVLO state. In this state, all the circuit is shut down. This state can only be cleared if VIN is supplied.

#### **PCB Layout Guideline**

- The high current paths (GND, VIN, VSYS and VCAP) should be placed very close to the IC with short, direct and wide traces.

- Put the input capacitors and VSYS capacitors as close to the VIN/VSYS and GND pins as possible.

- Keep the VIN and GND pads connected with large copper and use at least two layers for IN and GND trace to achieve better thermal performance. Also, add several vias with 10 mil\_drill/18 mil\_copper\_width close to the VIN and GND pads to help on thermal dissipation.

- Four-layer layout is strongly recommended to achieve better thermal performance.

# LS0502SCD33S

Single Cell Super Capacitor Protection IC for Backup Power Applications

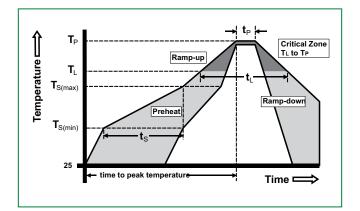

| Average Rar                | np Up Rate (Tsmin toT <sub>p</sub> )       | 1~2 °C/second, 3<br>°C/second max  |

|----------------------------|--------------------------------------------|------------------------------------|

|                            | - Temperature Min (T <sub>s(min)</sub> )   | 150 °C                             |

| Preheat &<br>Soak          | - Temperature Max (T <sub>s(max)</sub> )   | 200 °C                             |

| ooux                       | - Time (min to max) (t <sub>s</sub> )      | 60 – 120 seconds                   |

| Time<br>Maintained         | - Temperature(T <sub>L</sub> )             | 217 °C                             |

| Above                      | - Time(t <sub>L</sub> )                    | 60~150 seconds                     |

| Peak Temper                | rature (T <sub>P</sub> )                   | See classification temp in table 1 |

| Time Within<br>Temperature | 5 °C of Actual Peak<br>∋ (t <sub>p</sub> ) | 30 seconds max                     |

| Ramp-down                  | Rate                                       | 6 °C/second max                    |

| Time 25 °C t               | to Peak Temperature (T <sub>P</sub> )      | 8 minutes max                      |

Soldering Parameters

Note 1: Tolerance for peak profile temperature( $T_p$ ) is defined as a supplier minimum and a user maximum. Note 2: Tolerance for time at peak profile temperature ( $t_p$ ) is defined as a supplier minimum and a user maximum.

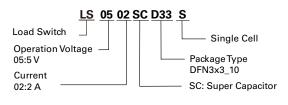

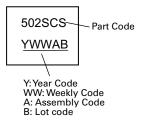

#### **Ordering Information**

| Part Number  | Marking | Package    | Min Order Qty    |

|--------------|---------|------------|------------------|

| LS0502SCD33S | 502SCS  | DFN3x3_10L | 5000/Tape & Reel |

### Part Numbering

# Table 1. Pb-free Process –Classification Temperatures (T<sub>c</sub>)

| Package<br>Thickness | Volume<br>mm <sup>3</sup><br><350 | Volume<br>mm <sup>3</sup><br>350-2000 | Volume<br>mm³<br>>2000 |

|----------------------|-----------------------------------|---------------------------------------|------------------------|

| <1.6 mm              | 260 °C                            | 260 °C                                | 260 °C                 |

| 1.6 mm–2.5 mm        | 260 °C                            | 250 °C                                | 245 °C                 |

| >2.5 mm              | 250 °C                            | 245 °C                                | 245 °C                 |

Note: For all temperature information, please refer to topside of the package, measured on the package body surface.

#### **Part Marking**

**11** Littelfuse

Inches

ΝЛ:

# LS0502SCD33S

Single Cell Super Capacitor Protection IC for Backup Power Applications

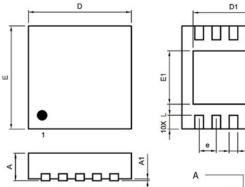

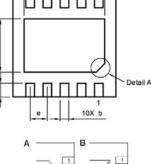

Dimensions - DFN3x3\_10L

Dimension

2

Detail A Theremal Pad Option

|    | IVIIII | IVIAX | IVIIII | IVIAX |

|----|--------|-------|--------|-------|

| А  | 0.70   | 0.80  | 0.028  | 0.031 |

| A1 | 0.00   | 0.05  | 0.000  | 0.002 |

| b  | 0.18   | 0.30  | 0.007  | 0.012 |

| D  | 2.90   | 3.10  | 0.114  | 0.122 |

| D1 | 2.10   | 2.60  | 0.083  | 0.102 |

| E  | 2.90   | 3.10  | 0.114  | 0.122 |

| E1 | 1.35   | 1.80  | 0.053  | 0.071 |

| е  | 0.50   |       | 0.0    | )20   |

| L  | 0.30   | 0.50  | 0.012  | 0.020 |

|    |        |       |        |       |

N/~

Millimeters

N/1:m

Recommended Land Pattern

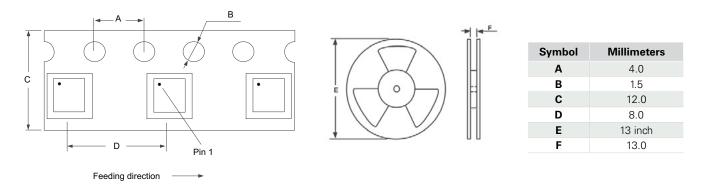

#### Carrier Tape & Reel Specification – DFN3x3\_10L

Product Disclaimer - Littelfuse products are not designed for, and shall not be used for, any purpose (including, without limitation, automotive, military, aerospace, medical, lifesaving, life-sustaining or nuclear facility applications, devices intended for surgical implant into the body, or any other application in which the failure or lack of desired operation of the product may result in personal injury, death, or property damage) other than those expressly set forth in applicable Littelfuse product documentation. Warranties granted by Littelfuse shall be deemed void for products used for any purpose not expressly set forth in applicable Littelfuse documentation. Littelfuse shall not be liable for any claims or damages arising out of products used in applications not expressly intended by Littelfuse as set forth in applicable Littelfuse documentation. The sale and use of Littelfuse products is subject to Littelfuse Terms and Conditions of Sale, unless otherwise agreed by Littelfuse. "Littelfuse" includes Littelfuse, Inc., and all of its affiliate entities.

https://www.littelfuse.com/legal/disclaimers/product-disclaimer.aspx