MPS CONFIDENTIAL AND PROPRIETARY / NO COPIES OR DISTRIBUTION WITHOUT MPS PERMISSION

# MP2755 Bi-directional 2:1/1:2 Switched Cap Converter With Shipping Mode Function

### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## DESCRIPTION

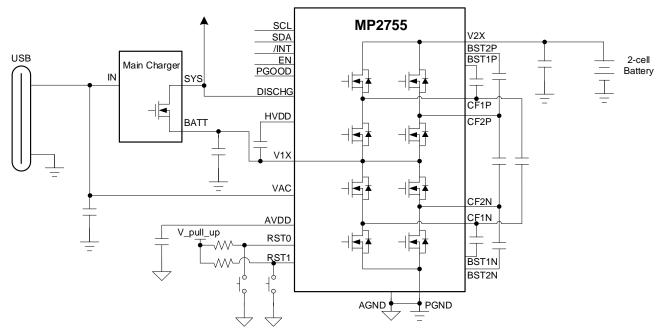

MP2755 is a highly-integrated bi-directional charging solution for 2-cell Li-ion or Li-polymer batteries. It employs an inductor-less switched cap architecture, can provide up to 10A output current in forward mode and 5A charging current in reverse mode.

The MP2755 is suitable for applications migrating from 1-cell battery to 2-cell configuration. Combined with a 2-cell battery, it can be treated as a virtual 1-cell battery, allowing the existing downstream 1-cell power architecture to be compatible with 2-cell battery pack.

The MP2755 integrates shipping mode function which can shut down V1X output with minimum battery current consumption. It also support system reset function.

The I<sup>2</sup>C interface offers complete operating control, charging / discharging parameter programming and status monitoring.

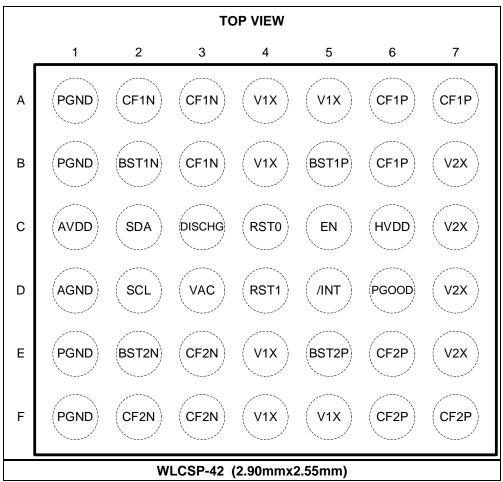

The MP2755 is available in a WLCSP-42 (2.90mm x 2.55mm) package.

# FEATURES

- Bi-directional switched capacitor converter

- Forward 2:1 conversion

- Reverse 1:2 conversion

- Dual-phase operation with 10A output current capability in forward direction

- 5A charge current capability in reverse direction

- Up to 99.3% efficiency

- Shipping mode and reset mode

- Audio mode to eliminate audible noise

- Dead battery activation power path

## APPLICATIONS

- Smart phones

- Tablet PCs

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

# TYPICAL APPLICATION

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **ORDERING INFORMATION**

| Part Number*    | Package                  | Top Marking | MSL Rating*** |

|-----------------|--------------------------|-------------|---------------|

| MP2755GC-xxxx** | WLCSP-42 (2.90mmx2.55mm) | See Below   | 4             |

| EVKT-MP2755     | Evaluation kit           | See Delow   | I             |

\* For Tape & Reel, add suffix -Z (e.g. MP2755GC-xxxx-Z).

\*\* "-xxxx" is the configuration code identifier for the register settings stored in the OTP register. Each "-x" can be a hexadecimal value between 0 and F. The default code is "-0000." Contact an MPS FAE to create this unique number.

\*\*\* Moisture Sensitivity Level Rating

# TOP MARKING

(TBD)

# PACKAGE REFERENCE

## MPS CONFIDENTIAL AND PROPRIETARY / NO COPIES OR DISTRIBUTION WITHOUT MPS PERMISSION

# MPS

# MP2755 – BI-DIRECTIONAL SWITCHED CAP CONVERTER WITH SHIPPING MODE

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## **PIN FUNCTIONS**

| Pin #                     | Name   | Type <sup>(1)</sup> | Description                                                                                                                        |

|---------------------------|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1, E1, F1            | PGND   | Р                   | Power ground.                                                                                                                      |

| A2, A3, B3                | CF1N   | Р                   | Flying capacitor 1 negative terminal.                                                                                              |

| F2, E3, F3                | CF2N   | Р                   | Flying capacitor 2 negative terminal.                                                                                              |

| A4, B4, A5,<br>E4, F4, F5 | V1X    | Р                   | Device power output.                                                                                                               |

| A6, B6, A7                | CF1P   | Ρ                   | Flying capacitor 1 positive terminal. Connect 3x47µF capacitor between CF1P and CF1N.                                              |

| E7, F6, F7                | CF2P   | Р                   | Flying capacitor 2 positive terminal. Connect 3x47µF capacitor between CF2P and CF2N.                                              |

| B2, C2, D2,<br>E2         | V2X    | Ρ                   | Device power input.                                                                                                                |

| C1                        | AVDD   | AO                  | LDO output. Connect a 4.7µF capacitor between this pin and GND.                                                                    |

| D1                        | AGND   | AIO                 | Analog ground.                                                                                                                     |

| B2                        | BST1N  | Ρ                   | Bootstrap capacitor for phase 1. Connect a 100nF/10V ceramic capacitor from BST1N to CF1N.                                         |

| E2                        | BST2N  | Р                   | Bootstrap capacitor for phase 2. Connect a 100nF/10V ceramic capacitor from BST2N to CF2N.                                         |

| G7                        | SDA    | DI                  | $I^2$ C interface data. Connect SDA to the logic rail through a pull up resistor (typical 10kΩ). The IC works as a slave.          |

| F7                        | SCL    | DIO                 | $I^2C$ interface clock. Connect SCL to the logic rail through a pull up resistor (typical 10k $\Omega$ ). The IC works as a slave. |

| C3                        | DISCHG | Р                   | Discharge pin in reset mode.                                                                                                       |

| D3                        | VAC    | AI                  | Input voltage sense pin.                                                                                                           |

| C4                        | RST0   | DI                  | Reset input 0. Active low. Do not float RST0.                                                                                      |

| D4                        | RST1   | DI                  | Reset input 1. Active low. Do not float RST1.                                                                                      |

| B5                        | BST1P  | Ρ                   | Bootstrap capacitor for phase 1. Connect a 100nF/10V ceramic capacitor from BST1P to CF1P.                                         |

| C5                        | EN     | DI                  | Enable pin.                                                                                                                        |

| D5                        | /INT   | DO                  | Open drain, active low interrupt output. Pull up to a logic rail with $10k\Omega$ resistor.                                        |

| E5                        | BST2P  | Р                   | Bootstrap capacitor for phase 2. Connect a 100nF/10V ceramic capacitor from BST2P to CF2P.                                         |

| C6                        | HVDD   | AO                  | Bootstrap capacitor for both phase 1 and phase 2. Connect a $1\mu$ F/10V ceramic capacitor from HVDD to V1X.                       |

| D6                        | PGOOD  | DO                  | Power good indicator output. High indicates the switched capacitor is switching.                                                   |

(1) AI = Analog Input, AO = Analog Output, AIO = Analog Input Output, DI = Digital Input, DO = Digital Output, DIO = Digital Input Output, P = Power

### MP2755 – BI-DIRECTIONAL SWITCHED CAP CONVERTER WITH SHIPPING MODE

### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## ABSOLUTE MAXIMUM RATINGS (1)

| VAC to PGND0.3V to +28V<br>V2X to PGND0.3V to +16V<br>V1X, DISCHG to PGND0.3V to +6V<br>CF1P, CF2P to PGND0.3V to +12V<br>CF1P, CF2P to V1X0.3V to +6V<br>CF1N, CF2N to PGND0.3V to +6V<br>HVDD to PGND0.3V to +11V<br>BST1P to CF1P, BST2P to CF2P0.3V to +5V<br>BST1N to CF1N, BST2N to CF2N0.3V to +5V<br>HVDD to V1X0.3V to +5V<br>EN to AGND0.3V to +16V |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST0, RST1 to AGND0.3V to +6V                                                                                                                                                                                                                                                                                                                                 |

| All Other Pins to AGND                                                                                                                                                                                                                                                                                                                                        |

| TBD<br>Junction temperature                                                                                                                                                                                                                                                                                                                                   |

### ESD Ratings

| Human body model (HBM) <sup>(3)</sup> . |                     |

|-----------------------------------------|---------------------|

| Charged device model (CDM)              | <sup>(4)</sup> 750V |

### **Recommended Operating Conditions** <sup>(5)</sup>

| Supply voltage (V <sub>VAC</sub> )          | Up to 20V       |

|---------------------------------------------|-----------------|

| V1X voltage (V <sub>OUT</sub> )             | Up to 5.5V      |

| V2X voltage (V <sub>OUT</sub> )             | Úp to 11V       |

| Operating junction temp (T <sub>J</sub> ) · | -40°C to +125°C |

Thermal Resistance  $^{(6)}$   $\theta_{JA}$   $\theta_{JC}$

WLCSP42 (2.90mm x 2.55mm)

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Per ANSI/ESDA/JEDEC JS-001, all pins.

- 4) Per ANSI/ESDA/JEDEC JS-002, all pins.

- 5) The device is not guaranteed to function outside of its operating conditions.

- 6) Measured on JESD51-7, 4-layer PCB.

**Notice:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third-party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.